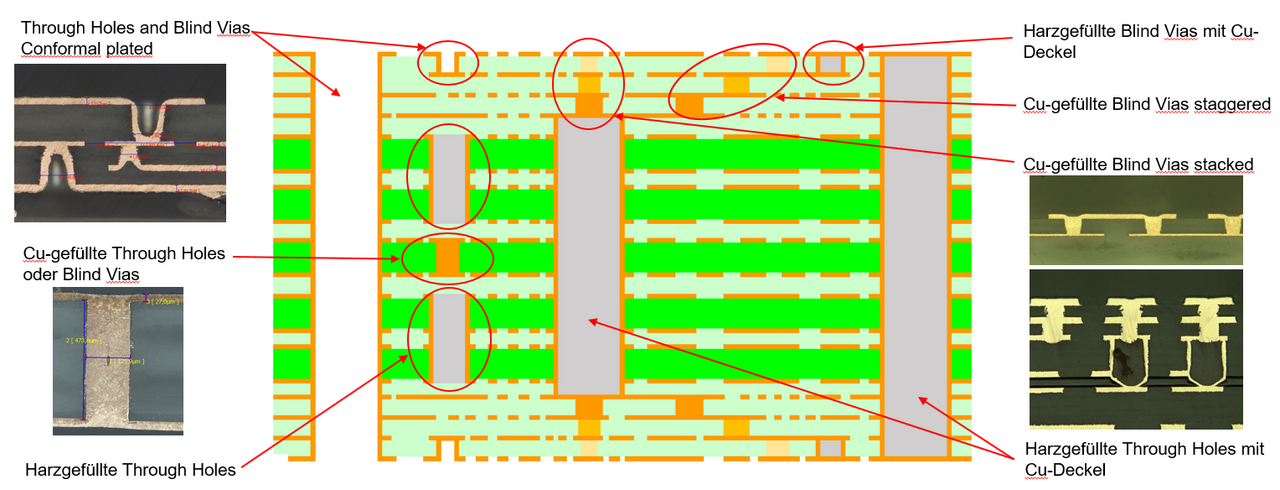

Auch wenn die Begrifflichkeiten Blind Via (Sackloch: Bohrung, die im Material endet) und Buried Via (Vergrabene Bohrung: Bohrung, die sich vollständig im inneren der PCB befindet) klar scheinen, so gibt es doch in der Branche uneinheitliche Sichtweisen zur Interpretation und den konkreten Ausführungen der verschiedensten Varianten.

Aus einer reinen Layout/Designsicht beinhaltet lediglich die außenliegende Lage Blind Vias, alle inneren Kontaktierungen werden als Buried Vias wahrgenommen und auch so bezeichnet. Aus einer technologischen Sichtweise aber wird auch die Kontaktierung zwischen L2 und L3 sowie L3 und L4 in der Fertigung als Blind Via-Lage produziert. Charakteristisch dafür ist, dass diese Bohrungen (Laser oder mechanisch) im Fertigungsprozess im Substrat enden und diese dann auch als Sacklöcher metallisiert werden. Im Fertigungsprozess vollständig durchbohrte Sub-Kerne (meistens mechanisch) bezeichnen wir als Buried Vias.

Da diese Prozess- und Fertigungssicht auch die kostenrelevante Sicht ist, beschreiben wir intern den Aufbau daher auch in dieser Weise.

Als Stacked Vias werden direkt übereinander gestapelte, sequentielle, lagenweise erzeugte Blind Vias bezeichnet. Dies ist ein probates Mittel, um bei höchster Packungsdichte zu entflechten und technologisch sicher beliebige Kontaktierungspfade zwischen den Layern zu erzeugen. Dazu werden jeweils Cu-Deckel oder Cu-gefüllte Vias als neue Landelage genutzt.

Beim sog. Anylayer wird von einer 2-seitig durchkontaktiertem Innenlage ausgehend, symmetrisch jede weitere Außenlage sequentielle aufgepresst und mit Blind Vias erneut angebunden. In Kombination mit o.g. Stacked Vias ist so jede elektrische Konfiguration ohne das Verpressen vorverarbeitete Sub-Kerne möglich.

| Beschreibung | Layoutvorgaben | Bemerkung | |

|---|---|---|---|

| A | Leiterbahnbreite | >=75µm | Abhängig von Cu-Dicke |

| B | Leiterbahnabstand | >=75µm | Abhängig von Cu-Dicke |

| Beschreibung | Layoutvorgaben | Bemerkung | |

|---|---|---|---|

| C | Leiterbahnbreite | >=75µm | Abhängig von Cu-Dicke |

| D | Leiterbahnabstand | >=75µm | Abhängig von Cu-Dicke |

| Beschreibung | Layoutvorgaben | Bemerkung | |

|---|---|---|---|

| E | Hole – Durchm. Eintritt | >=0,10mm | Wenn konisch, dann abhg. v. Bohrtiefe (Dielektrikumsdicke) |

| F | Hole – Durchm. Targetpad | >=0,10mm | Wird durch Werkzeug def. |

| G | Bohrtiefe | Dielektrikumsdicke Top-L2 | Aspect Ratio >1:1 beachten! |

| H | Micro Via Eintrittspad | >=E+200µm | Umlaufend 100µm um Bohrung nötig |

| I | Micro Via Landepad | >=350 µm | F+125µm umlaufend um Holedurchmesser auf Landepad |

| Beschreibung | Layoutvorgaben | Bemerkung | |

|---|---|---|---|

| J | Bohrdurchmesser | >0,10-6,05mm | |

| K | Bohrtiefe | <=J | Aspect Ratio >1:1 beachten! |

| Beschreibung | Layoutvorgaben | Bemerkung | |

|---|---|---|---|

| L | Bohrdurchmesser | >=0,15mm | Aspect Ratio >1:8 beachten! |

| M | Paddurchm. Außenlagen | >=L+200µm | Umlaufend 100µm um Bohrung nötig |

| N | Paddurchm. Innenlagen | >=L+250 µm | Umlaufend 125µm um Bohrung nötig |

| Eintrittsdurchmesser | Werkzeug | Dielektrika | Aspect Ratio |

|---|---|---|---|

| 0,10mm – 0,40mm | Standard oder konisch | Beliebig, Standard: FR4 | >=1:1 |

| 0,30mm – 0,55mm | Standard (α=130) | Beliebig, Standard: FR4 | >=1:1 |

| 0,55mm – 6,05mm | Standard (α=130) | Beliebig, Standard: FR4 | >=1:1 |

Regelmäßige Maschinen- und Prozessuntersuchungen sowie auftragsbezogene Einricht- und Schliffuntersuchungen sichern höchste Genauigkeit bei der Bohrtiefe, der Registrierung auf den Anbindungslagen sowie bei den Cu-Wandungsdicken der Vias.

Standardmäßig erfolgt unsere Fertigung auf Basis der Anforderungen der IPC-6010-Serie, Klasse 2, sowie die Qualitätsabnahme gemäß der IPC-A-600 (Abnahmekriterien für Leiterplatten), Klasse 2. Auf Wunsch produzieren wir auch gemäß Klasse 3 dieser Normen oder nach vorheriger Prüfung und Freigabe gemäß Ihrer kundenspezifischen Werksnorm.

Richtlinien zum prinzipiellen Aufbau von Multilayern entnehmen Sie bitte der Produkt-Info „Multilayer“, als Layoutrichtlinien, insbesondere zur Sacklochthematik, dienen Ihnen die Werte der Tabelle unter Punkt 2, „Begriffsklärung“.

Mit einem Laser oder mechanischen Werkzeugen werden elektrische Umsteigebohrungen, sog. Blind- und Buried Vias, zwischen den Multilayer-Lagen eingebracht und metallisiert. Unter Beachtung verschiedenster Design- und Layoutrichtlinien sind sie ein probates und notwendiges Mittel, um komplexe HDI/SBU-Multilayer zu fertigen.

Für weitergehende technologische Fragen rund um das Thema Leiterplatten wenden Sie sich bitte an unser CONTAG-Team (Tel. 030 / 351 788 – 0 oder team@contag.de).

Über mehrere Ebenen problemlos möglich

Auch größere Durchmesser als Sackloch problemlos realisierbar

Es können beliebige Dielektrikamaterialien verarbeitet werden

Höchste Anbindungszuverlässigkeit durch die Geometrie des Werkzeuges

Höchste Genauigkeit und Reproduzierbarkeit der Sacklochtiefe durch Kontaktbohren (+–15µm)

Hohe Wirtschaftlichkeit beim Prototyping

Für weitergehende technologische Fragen rund um das Thema BlindVias wenden Sie sich bitte an unser CONTAG-Team